### **Conference Program & Exhibitor Listings**

Don't miss out on electronic packaging's premier conference!

and Technology Conference

## May 30 - June 2, 2017

Walt Disney World Swan & Dolphin Resort Lake Buena Vista, Florida, USA

For more information, visit: www.ectc.net

Program Supported by:

Sponsored by:

### WELCOME FROM THE MAYOR OF ORANGE COUNTY

Orange County Mayor Teresa Jacobs

P.O. Box 1393 201 South Rosalind Ave, 5\* Floor Orlando, FL 32802-1393 Phone: 407-836-7370 Fax: 407-836-7360 Mayor@ocfl.net

May 2017

Greetings!

As Mayor of Orange County, it is my pleasure to welcome you to IEEE Electronic Components and Technology Conference 2017. We are honored that you chose the beautiful Walt Disney World Swan & Dolphin Hotel to host you event.

As you enjoy your time in Central Florida, I encourage you to see everything that our region has to offer. You will quickly discover why we continue to be the number one vacation destination in the nation with more than 66 million visitors in 2015. With our beautiful "Florida sunshine" providing the backdrop, you can discover our exciting theme parks, great cities and towns, excellent shopping opportunities, and relaxing parks and recreational amenities while experiencing superior hospitality and welcoming residents. These reasons, among many more, make Orange County a great place to live, work, and raise a family.

Our region is also home to top rated higher education institutions, the second largest convention center in the nation, and a burgeoning community of biotech, life sciences and research facilities, which have been recognized around the world for its forward thinking success. We are very proud of being a major international destination.

I wish you much success for your annual conference and hope that you enjoy your time here!

Sincerely.

Teresa Jacobs

### WELCOME FROM 67th ECTC GENERAL AND PROGRAM CHAIRS

On behalf of the Program Committee and Executive Committee, it is our pleasure to welcome you to the IEEE 67th Electronic Components and Technology Conference (ECTC), held at the beautiful Walt Disney World Swan & Dolphin Resort, Lake Buena Vista, Florida, from May 30 to June 2, 2017. All ECTC meetings and events will be taking place in the Dolphin building of the resort. This premier international conference of the global microelectronic packaging industry is sponsored by the IEEE Components, Packaging, and Manufacturing Technology (CPMT) Society.

The ECTC Program Committee has selected 335 papers that will be presented in 36 oral sessions and five interactive presentation sessions, including one interactive presentation session exclusively featuring papers by student authors. The oral sessions will feature selected papers on key topics such as flip chip packaging, 3D/TSV technologies, wafer level packaging, design for RF performance and signal/power integrity, thermal and mechanical modeling, optoelectronics packaging, and materials and reliability. Interactive presentation sessions will showcase papers in a format that encourages more in-depth discussion and interaction with authors about their work. Authors from 22 countries are expected to present their work at the 67th ECTC, covering ongoing technological challenges with established disciplines or emerging topics of interest for our industry, such as additive manufacturing, heterogeneous integration, and flexible and wearable electronics.

ECTC will also feature panel and special sessions with industry experts covering a number of important and emerging topic areas. On Tuesday, May 30 at 10 a.m., Vikas Gupta and Pradeep Lall will chair a session on "Material and Package Reliability Needs/Challenges for Harsh Environments." That same day at 2 p.m., Bing Dang will chair a panel session on "Flexible Hybrid Electronics – Electronics Outside the Box," where a panel of experts will discuss how innovation in device integration and packaging will bring together thinned silicon die with printed components to deliver electronics that conform to the shape of the human body and vehicles. Tuesday evening will also include the ECTC Panel Session at 7:30 p.m. on "Panel Fan-Out Manufacturing: Why, When, and How?" chaired by CPMT President Jean Trewhella and Young Gon Kim.

Babak Sabi, Corporate Vice President and Director of Assembly and Test Technology Development, Intel Corporation, will be giving the invited keynote talk on "Advanced Packaging Opportunities and Challenges" at the ECTC Luncheon on Wednesday, May 31. Later that day and continuing to build on the success of the first-ever CPMT Women's Panel and Reception held at the 65th ECTC two years ago, this year's conference will also feature a panel discussion chaired by Kitty Pearsall on Wednesday, May 31, at 6:30 p.m. on "Emotional Intelligence (El) – Link to Successful Leadership," with participation from distinguished women leaders and technologists in our industry. All conference attendees are invited. Also on Wednesday at 7:30 p.m., Luke England will chair the ECTC Plenary Session titled "Packaging for Autonomous Vehicle Electronics," featuring key technologists sharing their views on the evolutionary requirements for packaging and reliability challenges to support widespread implementation of self-driving vehicles on the road. On Thursday, June 1 at 8 p.m., the CPMT Seminar titled "3D Printing Tools, Technologies and Applications," will be moderated by Venkatesh Sundaram and Yasumitsu Orii from the High-Density Substrates & Boards Technical Committee of the CPMT Society.

Supplementing the technical program, ECTC also offers several Professional Development Courses (PDCs) and Technology Corner exhibits. Co-located with the IEEE ITherm Conference this year, the 67th ECTC will offer 18 PDCs, organized by the PDC Committee chaired by Kitty Pearsall. The PDCs will take place on Tuesday, May 30, and are taught by distinguished experts in their respective fields. The Technology Corner will showcase the latest technologies and products offered by leading companies in the electronic components, materials, packaging, and services fields. More than 100 Technology Corner exhibits will be open starting at 9 a.m. on Wednesday and Thursday. ECTC also offers attendees numerous opportunities for networking and discussion with colleagues during coffee breaks, daily luncheons, and nightly receptions.

Whether you are an engineer, a scientist, a manager, a student, or an executive, ECTC offers something unique for everyone in the microelectronics packaging and components industry. We would like to take this opportunity to thank all our sponsors, exhibitors, authors, speakers, PDC instructors, session chairs, program committee members, as well as all the volunteers who have helped to make the 67th ECTC another resounding success. Once again, thank you for being a part of the 67th ECTC.

Henning Braunisch

General Chair

Intel Corporation

Mark D. Poliks

Program Chair

Binghamton University

### WELCOME FROM ECTC SPONSORING ORGANIZATION

On behalf of CPMT, it is my great pleasure and privilege to welcome you to the 67th ECTC in Lake Buena Vista, Florida at the spectacular Walt Disney World Swan & Dolphin Resort!

The ECTC held its opening night 66 years ago and it hasn't missed a single year yet! Today, ECTC has become the premier international conference where professionals not only get a close-up look at every side of our industry, but also share research and development in technological breakthroughs across a wide

range of semiconductor packaging, electronics devices, design, materials, manufacturing, and modeling.

The CPMT Society is proud to be a sponsor of ECTC and present these program highlights:

• Opening Day: Tuesday, May 30, in addition to the ever popular Professional Development Courses there will be two special sessions: "Material and Package Reliability Needs/Challenges for Harsh Environments" chaired by Vikas Gupta and Pradeep Lall and "Flexible Hybrid Electronics – Electronics Outside the Box" chaired by Bing Dang. In the evening I will co-chair the ECTC CPMT Panel Session together with Young Gon Kim at 7:30 p.m. on "Panel Fan-Out Manufacturing: Why, When, and How?" Tuesday's program highlights the breadth and depth that ECTC delivers each year.

- To encourage diversity, networking, and professional development, CPMT will host a Women's Panel and Reception Wednesday at 6:30 p.m. on

"Emotional Intelligence Link to Successful Leadership," chaired by Kitty

Pearsall. All conference attendees are invited. CPMT will continue the

women's networking tables during the Wednesday and Thursday luncheons.

- On Thursday, June 1, CPMT will sponsor an award luncheon session to present several prestigious IEEE and CPMT awards.

- After the traditional Gala reception on Thursday evening the CPMT High-Density Substrates & Boards technical committee will host the seminar "3D Printing Tools, Technologies and Applications," moderated by Venkatesh Sundaram and Yasumitsu Orii.

Friday will feature sessions on topics that range from the reliability of fan-out WLP, automotive electronics and power module packaging to processing for 3D integration – all showing cutting edge advances in these critical areas.

Lastly I would like to take this opportunity to thank our dedicated volunteers on the ECTC program committee for their hard work over the past year. Also, appreciation goes to the session chairs, authors, speakers, and exhibitors who are instrumental to making the 67th ECTC a great success. As always I look forward to the impact all these technical and networking events will make on the CPMT Society, our industry, and our members.

Here's to four fast paced days of in-depth analysis, peer debate, and network expansion!

Jean Trewhella, President, IEEE CPMT Society

### **CONFERENCE POLICIES AND GUIDELINES**

#### Badges

Conference attendees MUST wear the official conference badge to be admitted to all training courses, sessions, meals, Technology Corner exhibits and all conference sponsored social functions.

### **Medical Services**

For emergency medical services, locate any hotel phone, whether in your room or elsewhere in the hotel, and follow its directions for emergencies. Hotel "house" phones have been placed throughout the hotel and conference area for your convenience. If no phone can be located, please locate the nearest hotel staff or ECTC staff for assistance with your emergency. The closest available hotel staff person may be at the front desk.

#### **Personal Property**

The hotel's safety deposit box is available for storing your valuables; particularly cash and jewelry. If there is a mini-safe in your room, you should consider using it.

### **Smoking Policy**

Smoking is NOT permitted in the hotel. Please follow hotel policies and signs regarding this. Smoking is also NOT permitted at any ECTC activities including, but not limited to, functions, events, sessions, and / or seminars. Thank you for your consideration and cooperation.

Recording presentations via photos or video is prohibited.

### **ECTC Mobile App**

ECTC is pleased to announce that a **free mobile app** is available again this year. The app provides information on schedules for our technical program and PDCs as well as exhibitors, sponsors, and general conference information and venue maps. The app also features tools to set your schedule so you don't miss presentations important to you, social interaction functions, and the ability to provide ratings on presentations that are used in selecting candidates for best paper awards. The app is available for iOS and Android devices from their respective app stores by searching "2017 ECTC". Look for login and password information on signage at ECTC! **All Oral Session Paper Ratings this year will be received only through this Mobile App.**

### **TABLE OF CONTENTS**

| Conference Policies & Guidelines                           | . 4 |

|------------------------------------------------------------|-----|

| ECTC Mobile App Information                                | . 4 |

| ECTC Luncheon Speaker                                      | 5   |

| iNEMI Committee Meetings.                                  | . 5 |

| CPMT Heterogeneous Integration Technology Roadmap Workshop | . 5 |

| Registration                                               | . 6 |

| PDC Instructors' and Proctors' Breakfast                   | . 6 |

| Session Chairs & Speakers Breakfast                        | . 6 |

| Speaker Prep Room                                          | 6   |

| Miscellaneous Information                                  | 6   |

| Luncheons                                                  | . 6 |

| ECTC Special Session                                       | 7   |

| Applied Reliability Special Session.                       | . 7 |

| CPMT Women's Panel & Reception                             | . 7 |

| ECTC Panel Session                                         | 7   |

| ECTC Plenary Session                                       | 7   |

| CPMT Seminar                                               | 7   |

| Professional Development Courses                           | . 8 |

| ECTC Student Reception                                     | . 8 |

| General Chair's Speaker Reception.                         | . 8 |

| Technology Corner Reception                                | . 8 |

| 67th ECTC Gala Reception                                   | . 8 |

| Continuing Education Units.                                | . 8 |

| 2016 ECTC Best Paper Awards                                | . 9 |

| Texas Instruments Best Student Paper                       | . 9 |

| Committee Meetings                                         | . 9 |

| Session 1: Fan-Out Packaging Process and Integration       | 10  |

|                                                            |     |

| Session 2: TSV Process, Characterization and Applications                   |

|-----------------------------------------------------------------------------|

| Session 3: Flip Chip Assembly                                               |

| Session 4: Advanced Substrates and Integrated Devices                       |

| Session 5: Emerging Sensors and Microsystems Packaging                      |

| Session 6: 5G, mmWave and Beyond                                            |

| Session 7: Fan-Out Packaging Materials and Passives                         |

| Session 8: Singulation Process Developments                                 |

| Session 9: Fine Pitch Flip Chip Process Technologies                        |

| Session 10: Harsh Environment Interconnect Reliability                      |

| Session 11: Mechanical Modeling and Characterization of Interposers and     |

| Interconnections                                                            |

| Session 12: Advanced Optical Components and Modules                         |

| Session 13: Interconnect Advances in FO & WLP                               |

| Session 14: Heterogeneous Integration                                       |

| Session 15: Flip Chip and Embedding in Substrates                           |

| Session 16: 3D Materials and Processing                                     |

| Session 17: Materials and Processes for Flexible and Wearable Devices 15 $$ |

| Session 18: Warpage, Electromigration and Mechanical Characterization 15 $$ |

| Session 19: Recent Advances in FOWLP Technology                             |

| Session 20: MEMS and Sensor Technologies                                    |

| Session 21: 3D Cu-Cu and Micro Bump Bonding Technologies                    |

| Session 22: Solder Joint & Interconnect Reliability, Characterization       |

| and Modeling                                                                |

| Session 23: Additive Manufacturing and Panel-Level Packaging                |

| Session 24: Novel Methods to Assess Reliability                             |

| Session 25: Characterization and Reliability of Fan-Out & WLP               |

| Session 26: 3D Integration Processing and Reliability                       |

| Session 27: Advances in Thermal Compression and Wirebonding |

|-------------------------------------------------------------|

| Session 28: Advanced Materials for Reliability Improvement  |

| Session 29: Warpage Control and Substrates                  |

| Session 30: RF Components and Module Integration            |

| Session 3 I: Auto Electronics Packaging and Power Modules   |

| Session 32: Reliability Challenges in 2.5D/3D Interconnect  |

| Session 33: Advanced Bonding and Soldering Technology       |

| Session 34: Waveguide Devices and Chip-to-Fiber Packaging   |

| Session 35: Thermomechanical and Thermal Characterization   |

| Session 36: Advances in Signal and Power Integrity          |

| Session 37: Interactive Presentations I                     |

| Session 38: Interactive Presentations 2                     |

| Session 39: Interactive Presentations 3                     |

| Session 40: Interactive Presentations 4                     |

| Session 41: Student Interactive Presentations               |

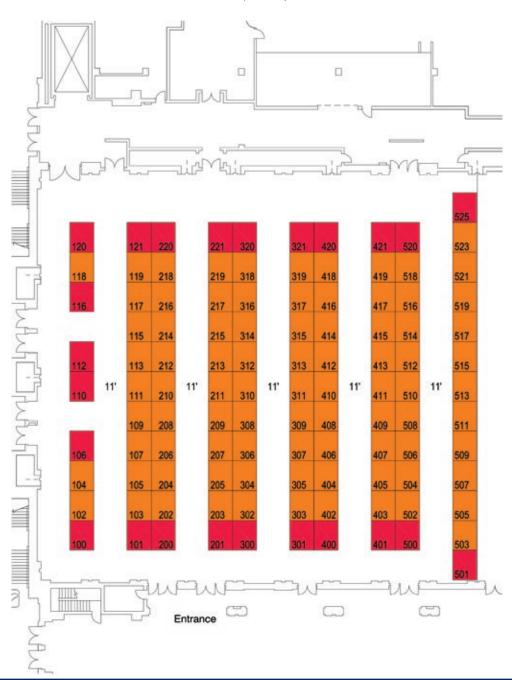

| Technology Corner Booth Layout                              |

| Technology Corner Exhibits                                  |

| ECTC Executive Committee                                    |

| ECTC Program Committee                                      |

| 68th ECTC Call for Papers                                   |

| Conference Sponsors                                         |

| Media Sponsors                                              |

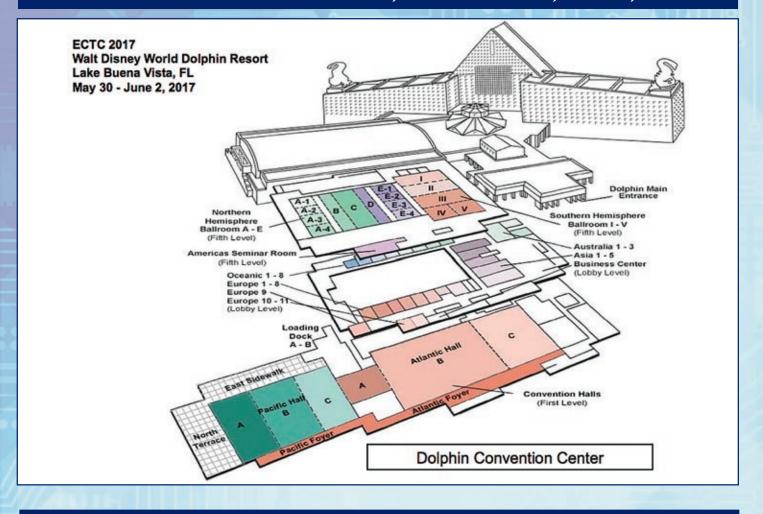

| Hotel Layout                                                |

| 68th ECTC Dates and Location                                |

| Conference at a Glance                                      |

### Conference organizers reserve the right to cancel or change this program without prior notice.

### **ECTC Luncheon Keynote Speaker**

Wednesday, May 31, 2017 12:00 Noon Northern Hemisphere D-E

Advanced Packaging Opportunities and Challenges

Presenter: Babak Sabi,

Corporate Vice President and Director

of Assembly and Test Technology

Development, Intel Corporation

Industry reliance on advanced packaging has been accelerating over the last few years. This trend is expected to continue in the future. Heterogeneous integration of multiple chips in a package supports Moore's Law scaling and is driving many challenges in package interconnect scaling, design environment, optical integration, electrical/thermal performance, and test. Babak Sabi, Corporate Vice President and Director of Assembly and Test Technology Development at Intel Corporation, will address future challenges and opportunities for advanced multi-chip packaging.

Since 2009, Babak has been responsible for Intel's packaging, assembly process, packaging materials, enabling technology, and test technology development. Prior to leading Assembly and Test Technology Development, Babak led the Corporate Quality Network within Intel's Technology and Manufacturing Group from 2002 to 2009. He also led a company-wide network of quality and reliability organizations responsible for product reliability, customer satisfaction, and quality business practices. Previously, Babak managed technology development quality and reliability, and was responsible for silicon technology certification, assembly, test, and board processes. Babak joined Intel in 1984, the same year he received his Ph.D. in solid state electronics from The Ohio State University.

### IEEE CPMT Heterogeneous Integration Technology Roadmap Workshop

Tuesday, May 30, 2017 • 8:00 a.m. - 5:00 p.m. Europe 4, Lobby Level

Our Industry has reinvented itself through multiple disruptive changes in technologies, products and markets. With the rapid migration of logic, memory and applications to the cloud infrastructures, the internet of things (IoT) to internet of everything (IOE), smart devices every where, and autonomous automotive, the pace of innovation is increasing to meet these challenges.

The Heterogeneous Integration Technology Roadmap (HIR), is sponsored by the IEEE CPMT Society, the Electron Devices Society (EDS), and Photonics Society together with SEMI and ASME EPPD. It will address the future directions of heterogeneous integration technologies and applications serving the future markets and applications, so very crucial to our societies' fields of interest and to our industries and academic and research communities. In addition to HIR, two other roadmaps are under development within IEEE: International Technology Roadmap for Wide Band-Gap Semiconductors (ITRW) sponsored by the IEEE Power Electronics Society (PELS), and International Technology Roadmap for Devices & Systems (IRDS), an IEEE Standards Association Industry Connection Program sponsored by the Rebooting Computing Initiative. Collaboration is underway to harmonize across the three roadmaps.

This HIR is our technology roadmap. The workshop will be held at the 2017 ECTC conference. We invite all the ECTC participants to attend this important working session for our profession and for our industry. The workshop is open to all. Registration is not necessary. There is no fee for attendance.

## iNEMI Technical & Research Committee Meeting

Tuesday, May 30, 2017 9:30 a.m. - 5:30 p.m. • Oceanic I - Lobby Level

By Invitation Only

### REGISTRATION, RECEPTIONS AND GENERAL INFORMATION

### Registration

ECTC registration will be open at the ECTC Registration Desk located in the Walt Disney World DOLPHIN Resort, Conference Center, Lobby Level, outside of Australia 3.

Monday, May 29, 2017 • 3:00 p.m. – 5:00 p.m.

Tuesday, May 30, 2017 • 6:45 a.m. - 8:15 a.m.\*

### (AM PD Courses & Special Session only)\*

Tuesday, May 30, 2017 • 8:15 a.m. – 5:00 p.m.

### (All conference attendees)

Wednesday, May 31, 2017 • 6:45 a.m. – 4:00 p.m.

Thursday, June 1, 2017 • 7:30 a.m. - 4:00 p.m.

Friday, June 2, 2017 • 7:30 a.m. – 12:00 Noon

\*The above schedule for Tuesday will be vigorously enforced to prevent students from being late for their courses. Please make sure to take advantage of the 6:45am start time on Tuesday, May 30 as registration becomes very congested prior to the start of morning Professional Development Courses.

### **Door Registration Fees**

| Door Registration with Proceedings on USB drive |               |

|-------------------------------------------------|---------------|

| IEEE Member JOINT Registration                  | <b>*</b> 1100 |

| (full ECTC + ITHERM conference)                 |               |

| IEEE Member Full Registration                   |               |

| IEEE Member Speaker / Session Chair             | \$730         |

| IEEE Member One Day                             | \$550         |

| IEEE Member Speaker One Day                     | \$415         |

| Exhibit Booth Attendant                         | \$0           |

| Non-Member JOINT Registration                   |               |

| (full ECTC + ITHERM conference)                 | \$1310        |

| Non-Member Full Registration                    |               |

| Non-Member Speaker / Session Chair              |               |

| Non-Member One Day                              |               |

| Non-Member Speaker One Day                      | \$415         |

| Exhibit Booth Attendant                         |               |

|                                                 |               |

| Student                                         |               |

| Student Speaker                                 | \$315         |

| Exhibits Only                                   | \$25          |

| Tuesday Professional Development Courses        |               |

| IEEE Members and Non-Members                    | <b>4500</b>   |

| Tuesday AM or PM Course with Luncheon           |               |

| Tuesday All-Day Courses with Luncheon           |               |

| Tuesday Student All-Day Courses with Luncheon   | \$130         |

| Extra Luncheon Tickets for Each Day             | \$65          |

| Extra Proceedings with Registration             |               |

### **Professional Development Course Instructors Breakfast**

PDC Instructors and Proctors are required to attend a briefing breakfast.

### 7:00 a.m. Tuesday - PDC Instructors and Proctor Briefing

(Room Location: Asia I, Lobby Level)

### Session Chairs and Speakers Breakfast

Session Chairs and speakers are required to attend a complimentary continental breakfast on the morning of their sessions/presentations. At this time, presentations will be transferred to the conference PC, which is loaded with Microsoft Windows and Office.

### 7:00 a.m. Wednesday thru Friday

(Room Location: Northern Hemisphere E 3 & 4, 5<sup>th</sup> floor)

### **Speaker Prep Room**

Speakers should prepare and review their digital presentations within the allotted times below:

### 7:00 a.m. - 5:00 p.m., Tuesday - Friday

(Room Location: Europe 2, lobby level)

(It is extremely important to assure that your presentation, presentation software and computer work flawlessly with the digital projector provided.)

### **MISCELLANEOUS INFORMATION**

### **Hotel Concierge**

The Hotel Concierge, located in the hotel lobby, can direct you to various types of entertainment or restaurants, or give suggestions for that special night out. The Concierge can help to make your visit and conference experience a memorable one!

### **Message Center**

Please use the hotel switchboard or the ECTC Registration Desk, located on the lobby level in the Australia 3 Foyer, to leave and pickup messages. The hotel phone number is +1 (407) 934-4000.

### **Press Room**

Press Interviews will be scheduled on an as-requested basis. To coordinate an interview with conference leadership or presenting technical experts please contact ECTC Publicity Chair, Eric Perfecto, at eric.perfecto@globalfoundries.com or +1 (845) 475-1290.

### **LUNCHEONS**

### Tuesday, May 30, 2017 12:00 Noon (Northern Hemisphere D / DE Corridor, 5th floor)

The Electronic Components and Technology Conference will sponsor a luncheon for all Professional Development Courses attendees, proctors and PDC committee members.

### Wednesday, May 31, 2017 12:00 Noon (Northern Hemisphere D & E, 5th floor)

The Electronic Components and Technology Conference will sponsor a luncheon for conference attendees. Best and Outstanding Papers will be awarded. The guest speaker will be Babak Sabi, Corporate Vice President and Director of Assembly and Test Technology Development, Intel Corporation.

### Thursday, June 1, 2017 12:00 Noon (Northern Hemisphere D & E, 5th floor)

The IEEE Components, Packaging and Manufacturing Technology Society will sponsor a luncheon for conference attendees. The CPMT awards will be presented.

### Friday, June 2, 2017 12:00 Noon (Northern Hemisphere D & E, 5th floor)

The ECTC Program Chair will sponsor a luncheon for conference attendees. You won't want to miss it!

There will be a raffle for attendees.

### 2017 ECTC SESSIONS & SEMINARS - Open to all conference attendees

2017 APPLIED RELIABILITY SPECIAL SESSION

Material and Package Reliability Needs/Challenges for Harsh Environments

Tuesday, May 30, 2017 10:00 a.m. – 11:30 a.m. Southern Hemisphere I, 5th Floor

Chairs: Vikas Gupta - Texas Instruments, Inc. and Pradeep Lall - Auburn University

#### Speakers:

- I. Robert Smith, Boeing Research & Technology

- 2. Przemyslaw Jakub Gromala, Bosch

- 3. Steve Dunford, Schlumberger

- 4. Anton Z. Miric, Heraeus Deutschland GmbH & Co. KG

- 5. Nancy Stoffel, General Electric

- 6. Varughese Mathew, NXP Semiconductors

### 2017 CPMT WOMEN'S PANEL AND RECEPTION

Emotional Intelligence (EI) - Link to Successful Leadership

Wednesday, May 31, 2017 6:30 p.m. – 7:30 p.m. Southern Hemisphere IV, 5th Floor

Chair: Kitty Pearsall - Boss Precision, Inc.

#### Speakers:

- I. Joanne Martin, JLM Consulting, LLC and former Vice President, IBM Corporation

- 2. Rozalia Beica, Global Director New Business Development, The Dow Chemical Company

- Tanja Braun, Deputy Group Manager, Fraunhofer Institute for Reliability and Microintegration IZM

### **2017 ECTC SPECIAL SESSION**

Flexible Hybrid Electronics – Electronics Outside the Box

Tuesday, May 30, 2017 2:00 p.m. – 3:30 a.m. Southern Hemisphere I, 5th Floor

Chair: Bing Dang - IBM Corporation

### Speakers:

- Benjamin Leever, Air Force Research

Laboratory, Materials & Manufacturing

Directorate

- James L. Zunino, U.S. Army RDECOM ARDEC

- 3. Robert Smith, Boeing Research & Technology

- 4. Girish Wable, Jabil

- 5. John Knickerbocker, IBM Corporation

### **2017 ECTC PLENARY SESSION**

Packaging for Autonomous Vehicle Electronics

Wednesday, May 31, 2017 7:30 p.m. – 9:00 p.m. Southern Hemisphere 11 & 111, 5th Floor

Chair: Luke England - GLOBALFOUNDRIES Speakers:

- I. Application and Market Projections Venky Sundaram, Georgia Institute of Technology

- 2. Powertrain Electronics Brent Richardson, Texas Instruments

- 3. Sensors Frank Bertini, Velodyne

- 4. Data Processing Dongji Xie, Nvidia

- 5. Wireless Communication Raj Pendse, Qualcomm Technologies, Inc.

### **2017 ECTC PANEL SESSION**

Panel Fan-Out Manufacturing: Why, When, and How?

Tuesday, May 30, 2017 7:30 p.m. – 9:00 p.m. Southern Hemisphere 11 & 111, 5th Floor

Chairs: Jean Trewhella, CPMT President -GLOBALFOUNDRIES and Young Gon Kim - Integrated Device Technology

### Speakers:

- I. Douglas Yu, TSMC

- 2. Tim Olson, DECA

- 3. Steffen Kroehnert, NANIUM

- 4. Rolf Aschenbrenner, IZM Fraunhofer

- 5. Steve Bezuk, Qualcomm Technologies, Inc.

#### **2017 CPMT SEMINAR**

3D Printing Tools, Technologies and Applications

Thursday, June 1, 2017 8:00 p.m. – 9:30 p.m. Southern Hemisphere 11 & 111, 5th Floor

Chairs: Venky Sundaram - Georgia Institute of Technology and Yasumitsu Orii - Nagase, Japan

### Speakers:

- 1. Manos Tentzeris, Georgia Institute of Technology

- 2. Humair Mandavia, Zuken SOZO Center

- 3. Simon Fried, Nano Dimension Ltd.

- 4. Takeshi Sato, Fuji Machine Mfg. Co., Ltd.

### PROFESSIONAL DEVELOPMENT COURSES • TUESDAY, MAY 30, 2017

All courses take place on the 5th floor unless otherwise noted.

#### Morning Courses 8:00 a.m. - 12:00 Noon Afternoon Courses 1:30 p.m. - 5:30 p.m. Northern Hemisphere El **Northern Hemisphere El** I. Achieving High Reliability of 10. Flip Chip Technologies Lead-Free Solder Joints - Material Course Leaders: Eric Perfecto – GLOBALFOUNDRIES; **Considerations** Shengmin Wen – Synaptics Inc. Course Leader: Ning-Cheng Lee - Indium Corporation **Northern Hemisphere E2** Northern Hemisphere E2 2. Wafer Level Chip Scale Packaging II. Package Failure Analysis - Failure Course Leader: Luu Nguyen – Texas Instruments, Inc. **Mechanisms and Analytical Tools** Course Leaders: Rajen Dias – Amkor Technology and Deepak Goyal – Intel Corporation **Northern Hemisphere E3 Northern Hemisphere E3** 3. LED Packaging, System, and 12. 3D IC Integration and 3D IC **Reliability Considerations** Course Leader: Xuejun Fan – Lamar University Course Leader: John Lau - ASM Pacific Technology Ltd. **Northern Hermisphere E4 Northern Hemisphere E4** 4. Future of Device and Systems **I3. Flexible Hybrid Electronics** Packaging: Strategic Technologies, Mfg. Course Leader: Pradeep Lall – Aubum University Infrastructure, and Applications Course Leader: Rao Tummala – Georgia Institute of Technology **Americas Seminar Americas Seminar** 14. Polymers for Electronic Packaging 5. Polymers and Nanocomposites for **Electronic and Photonic Packaging** Course Leader: Jeffrey Gotro - InnoCentrix, LLC Course Leaders: C. P. Wong - Georgia Institute of Technology; Daniel Lu – Henkel Corporation Southern Hemisphere III **Southern Hemisphere III** 6. Integrated Thermal Packaging and 15. Emerging Interconnect and System **Reliability of Power Electronics Integration Technologies** Course Leaders: Patrick McCluskey and Avram Bar-Course Leader: Muhannad Bakir – Georgia Institute of Cohen – University of Maryland Technology **Southern Hemisphere IV** Southern Hemisphere IV 7. Fundamentals of Electrical 16. Package Failure Mechanisms, **Design and Fabrication Processes of** Reliability, and Solutions Course Leader: Darvin Edwards - Edwards Interposers, Including Their RDLs Course Leaders: Ivan Ndip, Markus Wöhrmann, and Enterprises Michael Töpper – Fraunhofer IZM Southern Hemisphere V Southern Hemisphere V 17. Ageing of Polymers and the Influence 8. Introduction to Mechanics Based **Quality and Reliability Assessment** on Microelectronic Package Reliability Methodology Course Leaders: Tanja Braun and Ole Hölck -Course Leaders: Shubhada Sahasrabudhe and Fraunhofer IZM Sandeep Sane – Intel Corporation **Southern Hemisphere II** Southern Hemisphere II 9. Thermo-Electric Coolers: 18. Thermo-Electrical Co-Design of 3D Characterization, Reliability, and **Modeling** Course Leaders: Ankur Srivastava and Avram Bar-Cohen

### **ECTC STUDENT RECEPTION Tuesday, May 30, 2017** 5:00 p.m. - 6:00 p.m. Host: Texas Instruments, Inc.

Outside at the Cabana Deck by Dolphin Pool; (Rain Back Up – Asia I, Lobby Level)

ECTC welcomes our student attendees and student presenters who bring their research results to our audience. The Student Reception is an event where we provide guidance to students for their job search from industry leaders. In addition to the Student Reception, in the Student Interactive Presentation Session, we provide one-on-one access to students and their research to our audience. We encourage you to attend the Student Interactive Presentation Session on Friday. This reception is sponsored by Texas Instruments.

### **GENERAL CHAIR'S SPEAKERS RECEPTION** Tuesday, May 30, 2017 6:00 p.m. - 7:00 p.m.

Outside at the Crescent Terrace on the Swan Hotel side; (Rain Back Up – Northern Hemisphere D / DE Corridor)

Invited session chairs and speakers are requested to attend the reception.

### **TECHNOLOGY CORNER RECEPTION** Wednesday, May 31, 2017 5:30 p.m. - 6:30 p.m.

Northern Hemisphere A – C, 5<sup>th</sup> Floor

An Exhibitor Sponsored Reception will be held in Northern Hemisphere A - C, 5<sup>th</sup> Floor. All attendees and guests are invited.

### **67th ECTC GALA RECEPTION** Thursday, June 1, 2017 6:30 p.m.

Outside at the Lake Terrace on the Swan Hotel side; (Rain Back Up – Northern Hemisphere D – E)

All badged attendees and guests are invited to attend our Gala Reception outside at the Lake Terrace.

### CONTINUING EDUCATION UNITS

The IEEE Components, Packaging, and Manufacturing Technology Society (CPMT) has been authorized to offer Continuing Education Units (CEUs) by the International Association for Continuing Education and Training (IACET) for all Professional Development Courses that will be presented at the 67th ECTC. CEUs are recognized by employers for continuing professional development as a formal measure of participation and attendance in "non-credit" self-study courses, tutorials, symposia, and workshops. Complete details, including voluntary enrollment forms, will be available at the conference. All costs associated with ECTC Professional Development Course CEUs will be underwritten by the conference, i.e., there are no additional costs for Professional Development Course attendees to obtain CEU credit.

- University of Maryland, and Jim Wilson - Raytheon

Course Leader: Jaime Sanchez – Intel Corporation

### 2016 ECTC BEST PAPER AWARDS

### **BEST OF CONFERENCE PAPERS – 2016**

The Electronic Components and Technology Conference is proud to announce the "Best of Conference" papers selected from the 66th ECTC proceedings. The authors of the Best Session Paper share a check for US \$2,500 and the authors of the Best Interactive Presentation share a check for US \$1,500. The winning authors also receive a personalized plaque commemorating their achievement.

### **Best Session Paper**

Session 2, Paper 5

High-Frequency Analysis of Embedded

Microfluidic Cooling Within 3-D ICs Using a TSV

Testbed

Hanju Oh, Xuchen Zhang, Gary S. May, and Muhannad S. Bakir – Georgia Institute of Technology

### **Best Interactive Presentation**Session 37, Paper 2

Constitutive Relations for Finite Element Modeling of SnAgCu in Thermal Cycling – How Wrong We Were!

Thaer Alghoul, Dustin Watson, Nardeeka Adams, Saif Khasawneh, Farhan Batieha, Chris Greene, and Peter Borgesen — Binghamton University

### **INTEL BEST STUDENT PAPER – 2016**

The winning student receives a personalized plaque and a check for \$2,500. The following paper was selected based on the Intel Best Student Paper competition conducted at the 66th ECTC:

### Session 30, Paper 2

Non-Linear Finite Element Analysis on Stacked

Die Package Subjected to Integrated Vapor-HygroThermal-Mechanical Stress

Jing Wang and Seungbae Park, Binghamton University

### **OUTSTANDING PAPERS – 2016**

The winning authors for Conference Outstanding Session Paper and Interactive Presentation receive a personalized plaque commemorating their achievement and will share a check for US \$1,000.

### Outstanding Session Paper Session 13, Paper 4

**Eternal Packages: Liquid Metal Flip Chip Devices**

Assane Ndieguene, Pierre Albert, and Julien Sylvestre — Université de Sherbrooke; Clément Fortin and Valérie Oberson — IBM Corporation

## Outstanding Interactive Presentation Session 39, Paper 16

20" x 20" Panel Size Glass IPD Interposer Manufacturing

Yu-Hua Chen, Chun-Hsien Chien, Yu-Chung Hsieh, Wei-Ti Lin, Wen-Liang Yeh, Chien-Chou Chen, Dyi-Chung Hu, Tzyy-Jang Tseng — Unimicron Technology Corp. Hobie Yun — Qualcomm Technologies, Inc.

## TEXAS INSTRUMENTS OUTSTANDING STUDENT INTERACTIVE PRESENTATION — 2016

The winning student receives a personalized plaque and a check for US \$500. The following paper was selected based on the Texas Instruments Outstanding Student Interactive Presentation competition conducted at the 66th ECTC:

### Session 39, Paper 28

2D Grating Pitch Mapping of a Through Silicon Via (TSV) and Solder Ball Interconnect Region Using Laser Diffraction

Todd Houghton, Michael Saxon, Zeming Song, Hoa Nguyen, Hanqing Jiang, and Hongbin Yu - Arizona State University

### **COMMITTEE MEETINGS • ASSOCIATED COMMITTEE MEMBERS ONLY**

### **Tuesday, May 30, 2017**

9:30 a.m. - 5:30 p.m.

INEMI Meeting

Oceanic 1, Lobby Level

### 8:00 a.m. - 5:30 p.m.

IEEE CPMT Heterogeneous Integration Roadmap Workshop Europe 4, Lobby Level

### 9:00 p.m. - 10:30 p.m.

ECTC Interconnect Committee

Europe 4, Lobby Level

### Wednesday, May 31, 2017

7:00 a.m. - 8:00 a.m.

CPMT Materials & Processes TC Europe 3, Lobby Level

### 7:00 a.m. – 8:00 a.m.

CPMT Energy Electronics TC Europe 4, Lobby Level

### 4:30 p.m. - 5:30 p.m.

CPMT Technical Committee Chairs

Europe 1, Lobby Level

### 6:00 p.m. – 7:00 p.m.

Program Subcommittee Chairs & Assistant Chairs Reception General Chair's Suite (by invitation only)

### 9:00 p.m. - 10:30 p.m.

ECTC Opto Committee Americas Seminar, 5th Floor

### Thursday, June 1, 2017

7:00 a.m. - 8:00 a.m.

CPMT Region 8 Meeting Europe 4, Lobby Level

### 7:00 a.m. – 8:00 a.m.

CPMT RF & THz Technology TC Europe 5, Lobby Level

### 7:00 a.m. - 8:00 a.m.

CPMT High Density Substrates & Boards TC

Europe 1, Lobby Level

### 4:30 p.m. – 6:00 p.m.

CPMT Officers and Directors Meeting Oceanic 1, Lobby Level

### 5:30 p.m. – 6:30 p.m.

ECTC 2017 Program Committee Meeting Southern Hemisphere 1, 5th Floor

### 8:00 p.m.

67th ECTC Governing/Executive Committee Reception General Chair's Suite

### Friday, June 2, 2017

7:00 a.m. - 8:00 a.m.

CPMT Nanotechnology TC Europe 3, Lobby Level

### 7:00 a.m. - 8:00 a.m.

CPMT Thermal & Mechanical TC

Asia 1, Lobby Level

### 1:30 p.m. - 4:30 p.m.

ECTC Executive Committee

Europe 3, Lobby Level

### 4:45 p.m. - 5:45 p.m.

ECTC Steering Committee Europe 3, Lobby Level

| Session I: Fan-Out Packaging Process and Integration                                                                                                                                                                                                                                                                                                                                                                 | Session 2: TSV Process,<br>Characterization and Applications                                                                                                                                                                                                                                                                                | Session 3: Flip Chip Assembly                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Committee:<br>Advanced Packaging                                                                                                                                                                                                                                                                                                                                                                                     | Committee:<br>Interconnections                                                                                                                                                                                                                                                                                                              | Committee: Assembly & Manufacturing Technology                                                                                                                                                                                                                                                                                          |

| Room: Southern Hemisphere I                                                                                                                                                                                                                                                                                                                                                                                          | Room: Southern Hemisphere II                                                                                                                                                                                                                                                                                                                | Room: Southern Hemisphere III                                                                                                                                                                                                                                                                                                           |

| Session Co-Chairs:<br>Beth Keser – Intel Corporation<br>Mike Ma – Amkor Technology Taiwan (ATT)                                                                                                                                                                                                                                                                                                                      | Session Co-Chairs:<br>Takafumi Fukushima – Tohoku University<br>Tom Gregorich – SanDisk                                                                                                                                                                                                                                                     | Session Co-Chairs:<br>Valerie Oberson – IBM Corporation<br>Mark Gerber – Advanced Semiconductor<br>Engineering Inc.                                                                                                                                                                                                                     |

| I. 8:00 AM - Development of a Multi-<br>Project Fan-Out Wafer Level Packaging<br>Platform T. Braun, S. Raatz, U. Maass, M. van Dijk, H. Walter, O. Hölck, K. F. Becker, M. Töpper, R. Aschenbrenner - Fraunhofer IZM; M. Wöhrmann, S. Voges, M. Huhn, K. D. Lang – Technical University Berlin; M. Wietstruck, R.F. Scholz, A. Mai, M. Kaynak – IHP                                                                  | I. 8:00 AM - A Cost-Effective Via Last TSV<br>Technology Using Molten Solder Filling for<br>Automobile Application<br>Yuki Ohara, Yuki Inagaki, Masaki Matsui, and Kazushi<br>Asami – DENSO Corporation                                                                                                                                     | 1. 8:00 AM - Key Properties for Successful<br>Ultra Thin Die Pickup<br>Stefan Behler – Besi Switzerland AG; Teng Wang and<br>Arnita Podpod – IMEC                                                                                                                                                                                       |

| 2. 8:25 AM - SLIM <sup>TM</sup> , High Density Wafer<br>Level Fan-Out Package Development with<br>Submicron RDL<br>Youngrae Kim, JaeHun Bae, MinHwa Chang, AhRa Jo,<br>Ji Hyun Kim, SangEun Park, David Hiner, Mike Kelly,<br>and WonChul Do – Amkor Technology, Inc.                                                                                                                                                | 2. 8:25 AM - Accurate Depth Control of Through-Silicon Vias by Substrate Integrated Etch Stop Layers Matthias Wietstruck, Steffen Marschmeyer, Marco Lisker, Andreas Krueger, Dirk Wolansky, Philipp Kulse, Alexander Goeritz, Thomas Voss, Andreas Mai, and Mehmet Kaynak – IHP Microelectronics; Mesut Inac – Technical University Berlin | 2. 8:25 AM - Fine Pitch Cu Pillar with Bond<br>on Lead (BOL) Assembly Challenges for<br>Low Cost and High Performance Flip Chip<br>Package<br>Nokibul Islam, Vinayak Pandey, and KyungOe Kim –<br>STATS ChipPAC, Inc.                                                                                                                   |

| 3. 8:50 AM - Development of Novel High Density System Integration Solutions in FOWLP - Complex and Thin Wafer-Level SiP and Wafer-Level 3D Packages André Cardoso, Alberto Martins, Hugo Barros, Elisabete Fernandes, Abel Janeiro, Paulo Cardoso, and Leonor Dias - NANIUM S.A.                                                                                                                                     | 3. 8:50 AM - Application of a Metallic Cap<br>Layer to Control Cu TSV Extrusion<br>Golareh Jalilvand, Omar Ahmed, Keenan Bosworth,<br>Zhenlin Pei, Cullen Fitzgerald, and Tengfei Jiang –<br>University of Central Florida                                                                                                                  | 3. 8:50 AM - Improvement of C2W Collective Bonding Reliability and UPH through Innovations in Machine, Materials and Methods Tomonori Nakamura, Farhan Shafiq, Tetsuya Otani, Osamu Watanabe, Toru Maeda, and Yoshihito Hagiwara – Shinkawa Ltd.; Keiji Honjo, Daichi Mori, Outa Egashira, Daisuke Handa, and Tamotsu Owada – Dexerials |

| Refreshment Bre                                                                                                                                                                                                                                                                                                                                                                                                      | ak: 9:15 a.m 10:00 a.m. Northern                                                                                                                                                                                                                                                                                                            | Hemisphere A-C                                                                                                                                                                                                                                                                                                                          |

| 4. 10:00 AM - Fan-Out Chip on Substrate Device Interconnection Reliability Analysis lan Hu, Ying-Chih Lee, Wei-Hong Lai, Meng-Kai Shih, Chin-Li Kao, David Tarng, and Ching-Pin Hung – Advanced Semiconductor Engineering, Inc.                                                                                                                                                                                      | 4. 10:00 AM - Development of TSV Electro-<br>plating Process for Via-Last Technology<br>Gilho Hwang and Kalaiselvan Ravanethran – Institute<br>of Microelectronics, A*STAR                                                                                                                                                                  | 4. 10:00 AM - Thermo-Compression Bondin and Mass Reflow Assembly Processes of 3D Logic Die Stacks Pascale Gagnon, Christian Bergeron, Richard Langlois Stéphane Barbeau, Steve Whitehead, Katsuyuki Sakuma, Raphael Robertazzi, Christy Tyberg, Matthew Wordeman, and Michael Scheurmann – IBN Corporation                              |

| 5. 10:25 AM - Embedded Si Fan-Out: A Low-Cost Wafer Level Packaging Technology Without Molding and De-Bonding Processes Daquan Yu, Zhenrui Huang, Zhiyi Xiao, Li Yang, and Min Xiang – Huatian Technology (Kunshan) Electronics Co., Ltd.                                                                                                                                                                            | 5. 10:25 AM - Reliability Evaluation of Copper (Cu) Through-Silicon Via (TSV) Barrier and Dielectric Liner by Electrical Characterization and Physical Failure Analysis (PFA) Jiawei Marvin Chan and Chuan Seng Tan – Nanyang Technological University; Xu Cheng, Kheng Chooi Lee, and Werner Kanert – Infineon Technologies                | 5. 10:25 AM - Chip Shooter to Enable Fine Pitch Flip Chip Jie Fu, Manuel Aldrete, and Milind Shah – Qualcomm Technologies, Inc.                                                                                                                                                                                                         |

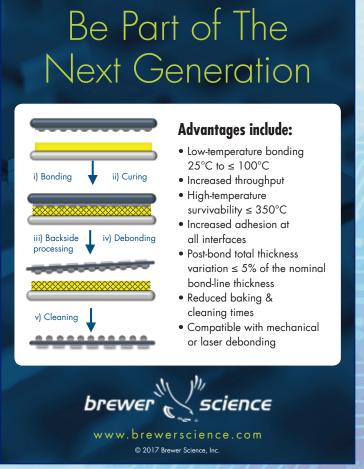

| 6. 10:50 AM - Process Development and Material Characteristics of TSV-Less Interconnection Technology for FOWLP Wen-Wei Shen, Yu-Min Lin, Hsiang-Hung Chang, Tzu-Ying Kuo, Huan-Chun Fu, Yuan-Chang Lee, Shu-Man Lee, Ang-Ying Lin, Shin-Yi Huang, Tao-Chih Chang — Industrial Technology Research Institute; Alvin Lee, Jay Su, Baron Huang, Dongshun Bai and Xiao Liu — Brewer Science; Kuan-Neng Chen Chen — NCTU | 6. 10:50 AM - Vertical Delay Modeling of Copper/Carbon Nanotube Composites in a Tapered Through Silicon Via  Madhav Rao – International Institute of Information Technology Bangalore                                                                                                                                                       | 6. 10:50 AM - Assembly Challenges for<br>75x75mm Large Body FCBGA with Emerging<br>High Thermal Interface Material (TIM)<br>Fletcher (Cheng-Piao) Tung, Max (Chin Yu) Lu,<br>Albert (Chang Yi) Lan, and Steward (Chi An) Pan –<br>Siliconware Precision Industries Co., Ltd.                                                            |

| 7. 11:15 AM - First Demonstration of Panel Glass Fan-Out (GFO) Packages for High I/O Density and High Frequency Multi-Chip Integration Tailong Shi, Vanessa Smet, Venky Sundaram, Rao Tummala, and Chintan Buch – Georgia Institute of Technology; Yoichiro Sato – Asahi Glass Co., Ltd.; Lutz Parthier – Schott;                                                                                                    | 7. II:15 AM - Latency, Bandwidth and Power Benefits of the SuperCHIPS Integration Scheme SivaChandra Jangam, Saptadeep Pal, Adeel Bajwa, Sudhakar Pamarti, Puneet Gupta, and Subramanian lyer – University of California, Los Angeles                                                                                                       | 7. 11:15 AM - Fine Pitch Interconnect<br>Rework for Lead-Free Flip Chip Packages<br>Malak Kanso, David Danovitch, and Elodie Nguena –<br>Sherbrooke University; Richard Langlois and Christian<br>Bergeron – IBM Corporation                                                                                                            |

| Program Sessions:                                                                                                                                                                                                                                                                                 | Wednesday, May 31, 8:00                                                                                                                                                                                                                                                                                                                  | a.m 11:40 a.m.                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Session 4: Advanced Substrates and Integrated Devices                                                                                                                                                                                                                                             | Session 5: Emerging Sensors and<br>Microsystems Packaging                                                                                                                                                                                                                                                                                | Session 6: 5G, mmWave and Beyond                                                                                                                                                                                                                                                                                                                                              |

| Committee:<br>Materials & Processing                                                                                                                                                                                                                                                              | Committee:<br>Emerging Technologies                                                                                                                                                                                                                                                                                                      | Committee:<br>High-Speed, Wireless & Components                                                                                                                                                                                                                                                                                                                               |

| Room: Southern Hemisphere IV                                                                                                                                                                                                                                                                      | Room: Southern Hemisphere V                                                                                                                                                                                                                                                                                                              | Room: Americas Seminar                                                                                                                                                                                                                                                                                                                                                        |

| Session Co-Chairs:<br>Tieyu Zheng – Microsoft Corporation<br>Yu-Hua Chen – Unimicron                                                                                                                                                                                                              | Session Co-Chairs:<br>Bharat Penmecha – Intel Corporation<br>Ramakrishna Kotlanka – Analog Devices                                                                                                                                                                                                                                       | Session Co-Chairs:<br>Kemal Aygun – Intel Corporation<br>Lih-Tyng Hwang – National Sun Yat-Sen<br>University                                                                                                                                                                                                                                                                  |

| I. 8:00 AM - A Novel Organic Substrate with Enhanced Thermal Conductivity Xiaoliang Zeng, Yimin Yao, Yougen Hu, Kun Guo, Jiajia Sun, and Rong Sun – Shenzhen Institutes of Advanced Technology; Jianbin Xu and Ching-Ping Wong – Chinese University Hong Kong                                     | I. 8:00 AM - Phototriggerable, Transient Electronics: Component and Device Fabrication Gerald Gourdin, Oluwadamilola Phillips, Jared Schwartz, Anthony Engler, and Paul Kohl — Georgia Institute of Technology                                                                                                                           | I. 8:00 AM - First Demonstration of 28 GHz and 39 GHz Transmission Lines and Antennas on Glass Substrates for 5G Modules Atom O. Watanabe, Muhammad Ali, Bijan Tehrani, Jimmy Hester, P. Markondeya Raj, Venky Sundaram, Manos M. Tentzeris, and Rao R. Tummala – Georgia Institute of Technology; Hiroyuki Matsuura – NGK Spark Plug; Tomonori Ogawa – Asahi Glass Co., Ltd. |

| 2. 8:25 AM - Infusing Inorganics into the Subsurface of Polymer Redistribution Layer Dielectrics for Improved Adhesion to Metals Shreya Dwarakanath, Pulugurtha Markondeya Raj, Collen Z. Leng, Venky Sundaram, Mark D. Losego, Rao R Tummala, and Vanessa Smet – Georgia Institute of Technology | 2. 8:25 AM - Novel High Temperature Capacitive Pressure Sensor Utilizing SiC Integrated Circuit Twin Ring Oscillators Maximilian C. Scardelletti, Philip G. Neudeck, David J. Spry, Roger D. Meredith, Jennifer L. Jordan, Norman F. Prokop, Michael J. Krasowski, Glenn M. Beheim, and Gary W. Hunter – NASA Glenn Research Center      | 2. 8:25 AM - Integrated Antenna-in-<br>Package on Low-Cost Organic Substrate for<br>Millimeter-Wave Wireless Communication<br>Applications<br>Cheng-Yu Ho, Ming-Fong Jhong, Po-Chih Pan, Chen-<br>Chao Wang, Chun-Yen Ting, and Chih-Yi Huang –<br>Advanced Semiconductor Engineering, Inc.                                                                                   |

| 3. 8:50 AM - Development of Solder Resist with Improved Adhesion at HTSL (175 deg C for 3000 Hours) and Crack resistance at TST for Automotive IC Package Chiho Ueta, Kazuya Okada, Toko Shiina, Tadahiko Hanada, and Nobuhito Itoh – Taiyo Ink Mfg. Co., Ltd.                                    | 3. 8:50 AM - An Experimental Magnesium Ion Battery Cell Made of Flexible Materials Todd Houghton, Gamal Eltohamy, and Hongbin Yu – Arizona State University                                                                                                                                                                              | 3. 8:50 AM - Aerosol-Jet Printed Quasi-<br>Optical Terahertz Filters<br>Christopher Oakley, Amanpreet Kaur, Jennifer<br>A. Byford, and Premjeet Chahal – Michigan State<br>University                                                                                                                                                                                         |

| Refreshment Bre                                                                                                                                                                                                                                                                                   | eak: 9:15 a.m 10:00 a.m. Northern                                                                                                                                                                                                                                                                                                        | Hemisphere A-C                                                                                                                                                                                                                                                                                                                                                                |

| 4. 10:00 AM - Bondable Copper Substrates With Silver Solid Solution Coatings for High-Power Electronic Applications Yongjun Huo and Chin C. Lee – University of California, Irvine                                                                                                                | 4. 10:00 AM - Fractal-Structured, Wearable Soft Sensors for Control of a Robotic Wheel- chair via Electrooculograms Saswat Mishra, Yongkuk Lee, Dong Sup Lee, and Woon-Hong Yeo – Virginia Commonwealth University                                                                                                                       | 4. 10:00 AM - High Performance Chip-Partitioned Millimeter Wave Passive Devices on Smooth and Fine Pitch InFO RDL Che-Wei Hsu, Chung-Hao Tsai, Jeng-Shien Hsieh, Kuo-Chung Yee, Chuei-Tang Wang, and Douglas Yu – Taiwan Semiconductor Manufacturing Company, Ltd.                                                                                                            |

| 5. 10:25 AM - On-Chip Integrated Solid-<br>State Micro-Supercapacitor<br>Muhammad Amin Saleem, Rickard Andersson, and<br>Vincent Desmaris – Smoltek AB; Bo Song and C.P<br>Wong – Georgia Institute of Technology                                                                                 | 5. 10:25 AM - Micro-Hermetic Packaging<br>Technology for Active Implantable Neural<br>Interfaces<br>Kaustubh Nagarkar, Nancy Stoffel, Eric Davis, and<br>Jeffrey Ashe – General Electric Co.; Xiaoxiao Hou and<br>David Borton – Brown University                                                                                        | 5. 10:25 AM - Directional Through Glass<br>Via (TGV) Antennas for Wireless Point-to-<br>Point Interconnects in 3D Integration and<br>Packaging<br>Seahee Hwangbo, Hyowon An, Sheng-Po Fang, and<br>Yong-Kyu Yoon – University of Florida; Aric B. Shorey<br>and Abbas M. Kazmi – Corning, Inc.                                                                                |

| 6. 10:50 AM - Development of CPU Package Embedded with Multilayer Thin Film Capacitor for Stabilization of Power Supply Tomoyuki Akahoshi, Daisuke Mizutani, Kei Fukui, Seigo Yamawaki, Hidehiko Fujisaki, Manabu Watanabe, and Masateru Koide – Fujitsu Laboratories, Ltd.                       | 6. 10:50 AM - Biopackaging of Minimally Invasive Ultrasound Assisted Clot Lysis Device for Stroke Treatment Ramona Damalerio, Ming-Yuan Cheng, Weiguo Chen, Liang Lou, and Songsong Zhang – Institute of Microelectronics, A*STAR                                                                                                        | 6. 10:50 AM - RF Characterization and<br>Modeling of 10 µm Fine-Pitch Cu-Pillar on a<br>High Density Silicon Interposer<br>Hélène Jacquinot, L. Arnaud, A. Garnier, F. Bana, J.C.<br>Barbe, and S. Cheramy – CEA-Leti                                                                                                                                                         |

| 7. 11:15 AM - Panel-Based Integrated Passive Device for RF Application Ming Hung Chen, Tze Hsin Chiang, Jia Hao Zhang, Hsu Chiang Shih, Sheng Chi Hsieh, Teck Chong Lee, and Chih Pin Hung – Advanced Semiconductor Engineering, Inc.                                                             | 7. II:15 AM - A Low-Profile Flow Sensing System for Monitoring of Cerebrospinal Fluid with a New Ventriculoamniotic Shunt Yanfei Chen, Stephanie Greene, Puneeth Shridhar, and Youngjae Chun – University of Pittsburgh; Connor Howe and Woon-Hong Yeo – Virginia Commonwealth University; Emery Stephen – Magee-Womens Hospital of UPMC | 7. II:15 AM - Miniature 2.4-GHz Switched<br>Beamformer Module in IPD and its<br>Application to Very-Low-Profile ID and 2D<br>Scanning Antenna Arrays<br>Chia-Hao Chen, Wei-Ting Fang, and Yo-Shen Lin –<br>National Central University                                                                                                                                        |

| Program Sessions                                                                                                                                                                                                                                                                                                                                                   | : Wednesday, May 31, 1:30                                                                                                                                                                                                                                           | р.т 5:10 р.т.                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Session 7: Fan-Out Packaging Materials and Passives                                                                                                                                                                                                                                                                                                                | Session 8: Singulation Process Developments                                                                                                                                                                                                                         | Session 9: Fine Pitch Flip Chip Process<br>Technologies                                                                                                                                                                                                                                                                                                                                                                             |

| Committee:<br>Advanced Packaging                                                                                                                                                                                                                                                                                                                                   | Committee: Assembly & Manufacturing Technology                                                                                                                                                                                                                      | Committee:<br>Interconnections                                                                                                                                                                                                                                                                                                                                                                                                      |

| Room: Southern Hemisphere I                                                                                                                                                                                                                                                                                                                                        | Room: Southern Hemisphere III                                                                                                                                                                                                                                       | Room: Southern Hemisphere II                                                                                                                                                                                                                                                                                                                                                                                                        |

| Session Co-Chairs:<br>Luke England – GLOBALFOUNDRIES<br>Bora Baloglu – Amkor Technology                                                                                                                                                                                                                                                                            | Session Co-Chairs:<br>Garry Cunningham – NGC<br>Li Jiang –Texas Instruments                                                                                                                                                                                         | Session Co-Chairs: David Danovitch – University of Sherbrooke Li Li – Cisco Systems, Inc.                                                                                                                                                                                                                                                                                                                                           |

| I. 1:30 PM - Development of Liquid, Granule, and Sheet Type Epoxy Molding Compounds for Fan-Out Wafer Level Package Kenichi Ueno, Kazuhiro Dohi, Kazuyoshi Muranaka, Akira Nakao, and Yuki Ishikawa – Sanyu Rec Co., Ltd.                                                                                                                                          | I. I:30 PM - Expanding Film and Process for<br>High Efficiency 5 Sides Protection and FO-<br>WLP Fabrication<br>Kazutaka Honda, Naoya Suzuki, Toshihisa Nonaka,<br>Hirokazu Noma, and Yoshinobu Ozaki – Hitachi<br>Chemical Co., Ltd.                               | I. I:30 PM - Cu-SnAg Interconnects Evaluation for the Assembly at 10µm and 5µm Pitch Divya Taneja, Marion Volpert, Gilles Lasfargues, Boris Bouillard, Aurelie Vandeneynde, Tarik Chaira, Yannick Goiran, David Henry, Bertrand Chambion, and Sylvie Jarjayes - CEA-Leti; Fiqiri Hodaj - University Grenople Alps, SIMAP                                                                                                            |

| 2. 1:55 PM - Ultra-Low Temperature FOWLP Process for the Embedding of Low Thermal Budget Sensors and Components Using SU-8 as Dielectric Raquel Pinto, André Cardoso, Sara Ribeiro, and Carlos Brandão — NANIUM S.A.; João Gaspar, Rizwan Gill, Helder Fonseca, and Margaret Costa — INL; Filipe Cardoso and Mariana Antunes — Magnomics                           | 2. 1:55 PM - Laser Multi Beam Full Cut Dicing of Wafer Level Chip-Scale Packages Jeroen van Borkulo, Eric Tan, and Richard van der Stam – ASM Pacific Technologies                                                                                                  | 2. 1:55 PM - Scaling Cu Pillars to 20µm Pitch<br>and Below: Strategic Role of Surface Finish<br>and Barrier Layers<br>Ting-Chia Huang, Vanessa Smet, Pulugurtha<br>Markondeya Raj, and Rao Tummala – Georgia Institute<br>of Technology; Robin Taylor, Gustavo Ramos, Rick<br>Nichols, Arnd Kilian, and Maja Tomic – Atotech                                                                                                        |

| 3. 2:20 PM - Integrated Copper Heat Slugs and EMI Shields in Panel Laminate (LFO) and Glass Fan-Out (GFO) Packages for High Power RF ICs  Venky Sundaram, Bartlet Deprospo, Nahid Gezgin, Atomu Watanabe, P. Markondeya Raj, Fuhan Liu, Waylon Puckett, Samuel Graham, and Rao Tummala – Georgia Institute of Technology; Kyle Byers and Sean Garrison – Honeywell | 3. 2:20 PM - Plasma Dicing 300mm Framed Wafers - Analysis of Improvement in Die Strength and Cost Benefits for Thin Die Singulation Richard Barnett – SPTS Technologies, Ltd.                                                                                       | 3. 2:20 PM - Thermal Compression Bonding:<br>Understanding Heat Transfer by in situ<br>Measurements and Modeling<br>Pieter Bex, Teng Wang, Vladimir Cherman, Melina<br>Lofrano, Giovanni Capuz, Erik Sleeckx, and Eric Beyne<br>– IMEC                                                                                                                                                                                              |